SEP

Digital Signal Processing Quiz

Test your knowledge on digital signal processing with our comprehensive quiz. Covering a range of topics, this quiz is ideal for students, teachers, and professionals looking to refresh their understanding.

- Questions covering interrupt vectors and addressing modes.

- Insights into DSP architecture and instruction sets.

- Special features relevant to DSPs in assemblers.

Un vector de intrerupere

Stabilete legatura intre sursa intreruperii si subrutina de tratare asociata

Are, de regula, o lungimme de unul sau doua cuvinte si este localizarta in zona inferioara de memorie

Este asociat fiecarei surse de intrerupere

Nu exista in cazul DSP-urilor

Din ce categorie de moduri de adresare face parte instructiunea "A6=A6+*R6", care are ca efect adunarea valorii stocate la locatia de memorie indicata de continutul registrului R6 la valoarea stocata in registrul acumulator A6:

Adresare indirecta cu registru

Adresare indirecta cu registru cu indexare

Adresare indirecta cu registru cu pre sau post incrementare

Adresare indirecta cu registru cu adresare modulo

In cadrul DSP-urilor cu pipeline exista urmatoarele modele de programare care folosesc limbaj de asamblare:

Doar modelul de programare cu timp stationar

Doar modelul de prograare cy date de stationare

Modelul de programare cu timp stationar si modelul de programare cu date stationare

Un exista astfel de model de programare

Modulul de adresare care foloseste un buffer cicrular de tip FIFO este:

Adresare indirecta cu registru

Adresare indirecta cu registru cu prea sau post incrementare

Adresare indirecta cu registru cu indexare

Adresare indirecta cu registru cu adresare modulo

Care din afirmatiile referitoare la setul de instructiuni de rotatie ale procesoarelor de semnal sunt adevarate:

Operatiile de rotatie stanga/dreapta se executa cu un singur bit

Operatiile de rotatie stanga/dreapta se executa cu minim 2 sau 4 biti

Pot fi considerate operatii de deplasare circulara

Nu exista astfel de operatii la procesoarele de semnal

Ortogonalitatea setului de instructiuni:

Nu exista in cazul DSP-urilor

Este influentata doar de gradul in care modurilor de adresare sunt disponibile in mod in mod uniform pentru diverse operatii efectuate de procesor

Nu poate fi masurata

Este influentata de consistenta si gradul in care modurile de adresare sunt disponibile in mod uniform pentru diverse operatii efectuate de procesor

In cazul procesoarelor de semnal, relaizarea stivei poate fi efectuata prin urmatoarele metode:

Stiva cu set specializat de registre

Stiva software cu registru de memorare al varfului stivei

Stiva hardware cu memoria RAM

Niciun raspuns dat

Care din urmatoarele facilitati sunt specifice procesoarelor de semnal pentru executia buclelor?

Bucl hardware pentru execitia buclelor fara cicluri masina suplimentari

Registre speciale pe post de contur de bucla

Instructiuni de salt (software)

Sunt identice cu cele de la procesoarele de uz general

Porturile gazda intalnite la procesoarele de semnal:

Sunt porturi serial bidirectionale specializate pe 8 biti sau de 16 biti

Sunt porturi unidirectionale nespecializate

Lucreaza in regim DMA in mod uzual (data prezenta la port este scrisa automat in memoria procesorului de semnal fara a-l opri, cu sau fara intreruperi)

Nu poate fi folosit pentru a controla procesorul digital de semnal(nu poate sa-l forteze sa execute instructiuni sau rutine de serviciu de intrerupere, sa citeasca sau sa scrie registre/memoria, etc. )

Pipeline-ul mareste de obicei timpul de raspuns al procesorului la intreruperi:

Cand executia saltului nu exista

Cu cat executia saltului este mai intarziata

Cu cat executia salutului este mai rapida

Toate variantele sunt corecte

Penrtu programe ce pot fi rulate indiferent de adresa este folosit saltul:

Intarziat cu anulare

Relativ la PC

Conditionat

Neconditionat

Registrii ce se pot utiliza ca operanzi pentru majoritatea operatiilor aritmetice si de multiplicare sunt

Registri acumulatori

Registrul de uz general

Numaratorul de program

Registrii pentru adresa

In logica pozitiva la circuitelor de interfata generala

O tensiune pozitiva pe linia seriala de date reprezinta un "0" logic, iar o tensiune scazuta (apropae 0) reprezinta "1" logic

O tensiune pozitiva pe linia seriala de date reprezinta un "1" logic, iar o tensiune scazuta (apropae 0) reprezinta "0" logic

O tensiune negativa pe linia seriala de date reprezinta un "0" logic, iar o tensiune scazuta (apropae 0) reprezinta "1" logic

O tensiune negativa pe linia seriala de date reprezinta un "1" logic, iar o tensiune scazuta (apropae 0) reprezinta "0" logic

Stiva ce contine starea registrilor selectati in timpul apelurilor subrutinelor este

Nici una

Shadow registers

Stiva software

Stiva hardware

Familia de procesoare Texas Instruments similara facilitatilor microcontrolerelor este

TSM320C4000

TSM320C5000

TSM320C6000

TSM320C2000

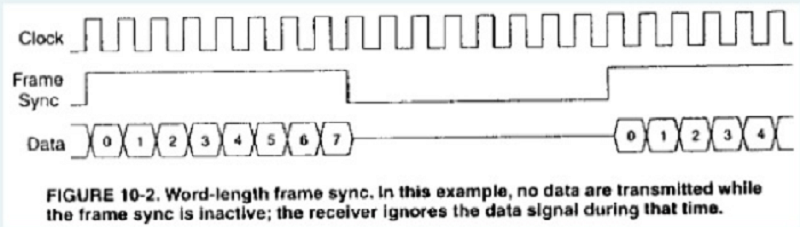

In fig este reprezentat un semnal de sincronizare de cadre de tip

"big length" si un singur cuv de date per cadru

"big length" si cuv multiple de date per cadru

"word length" si un singur cuv de date per cadru

"word length" si cuv multiple de date per cadru

Secventa de program afiseaza un model de programare: AO =AO+P P=X*Y Y=*RO ++ P=*Pt+ +

Cu date stationare si cu timp stationar

Cu timp stationar

Nicio varianta

Cu date stationare

La procesoarele ce pot realiza imbricarea directa, adancimea de intrepatrundere poate avea:

Patru nivele

Opt nivele

Doua nivele

Un nivel

Care este metoda de management a energiei in care ceasul este oprit la rnajoritatea sectiunilor procesorului:

Controlul frecventei ceasului

Modul adorrmit

Perifericele si controlul operatiilor 1/0

Dezactivarea pinilor de ie?ire de ceas nefolositi

Secventa de cod prezinta o bucla pentru: RPT #16 MAC (RO)+, (R4)+, A

IIR implementat in limbaj de asamblare cu cicluri asistate hardware

IIR irnplementat in limbaj de asarnblare cu ciclu ri asistate software

FIR implernentat in limbaj de asamblare cu cicluri asistate software

FIR irnplementat in limbaj de asamblare cu cicluri asistate hardware

Aplicarea unui factor de prescalare cu valoarea 4:

Mareste perioada de doua ori

Mareste frecventa de patru ori

M icsoreaza perioada de doua ori

Micsoreaza frecventa de patru ori

La procesoarele care nu accepta operatia de inversare a bitilor irnplementata in unitatea de generare a adreselor, pentru generarea adreselor cu bitii inversati este utilizata:

Deplasarea

Comparatia

Lnstructiuni cu executie conditionata

Rotatia

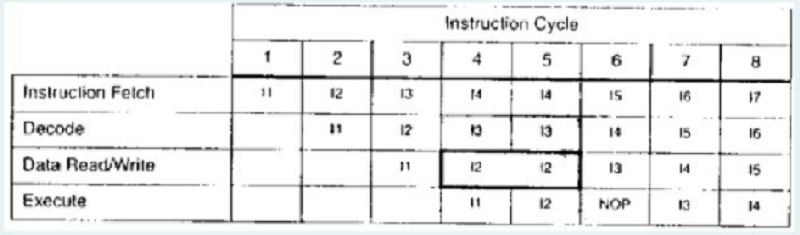

Presupunand ca fiecare etapa din figura necesita pentru a fi executata aproximativ 10ns, fn cat timp este executata 13:

40ms

30ns

40ns

50ns

Bitu l ce indica daca rezultatul ultin1ei operatii aritrnetice a fost nul se nume?te:

Bit de zero

Bit de transport

Bit de depasire

Bit de minus

Portul dedicat pentru cornunicarea cu un microprocesor de uz general este denumit:

Port 1/0 de bit

Port gazda

Port paralel

Circuit tirner

Procesoarele Tn virgula fixa au:

Cost mai ridicat

Gama dinarnica ridicata

Programarea mai facila fata de procesoarele cu virgula mobila

Arhitectura de sistem mai putin complexa fata de procesoarele cu virgula mobila

Consumul de energie in circuitele CMOS:

Scade cu cre?terea tensiunii

creste liniar cu tensiunea

Creste liniar cu frecventa de tact

este invers proportional cu patratul tensiunii

Instructiunile de salt pot avea urmatoarele forme suportate de diverse procesoare de semnal:

Multiciclu (saltul se executa dupa o intarziere de cateva cicluri)

Saltul intarziat cu anulare (instructiunile aflate dupa instructiunea de salt pot anula saltul, dad anumite conditii nu sunt indeplinite)

Conditionat (sa execute saltul doer dace este indeplinita una sau mai multe conditii) si neconditionat (saltul se executa mereu)

Intarziat (permite procesorului sa execute cateva instructiuni aflate dupa instructiunea de salt, inainte ca saltul sa fie executat efectiv)

Din ce categorie de moduri de adresare face parte instructiunea „MLR a", care are ca rezultat AX=AL*a, unde AX si AL sunt registrele procesorelui folosite implicit pentru operatia de inmultire si „a" este o variabilar oarecare pe 8 biti:

Adresare directs la memorie

Adresare implicita

Adresare imediata

Adresare directa la registru

Tensiunea de alimentare nominala a unui procesor de semnal este descrisa ca fiind Vcc=5V +1- 5%. Care din urmatoarele tensiuni se incadreaza in plaja data:

4.65

5.28

5.40

4.85

In cazul executiei instructiunilor in pipeline, hazardul poate fi eliminat prin:

Reordonarea instructiunilor prin incarcarea lor intr-un buffer de instructiuni si executia lor in mod dinamic

Q b. Hazardul din pipeline nu poate fi eliminat

Avansarea datelor (rezultatelor) intre instructiuni si Intre etapele pipeline-ului

Eliminarea dependentei de date prin introducerea de NOP-uri intre instructiunile care depind de aceleasi date

In cazul interfetelor seriale asincrone datele sunt insotite de un semnal de ceas suplimentar

Adevarat

Fals

La aparitia unei intreruperi, aproape toate procesele permit terminarea instructiunilor aflate in stadiul de incarcare

Adevart

Fals

Intreruperile ca urmare a unei depasiri de scala sunt

Intreruperi de la linii externe

Intreruperi de la periferice incorporate

Intreruperi software

Intreruperi pentru cod ilegal

{"name":"SEP", "url":"https://www.quiz-maker.com/QPREVIEW","txt":"Test your knowledge on digital signal processing with our comprehensive quiz. Covering a range of topics, this quiz is ideal for students, teachers, and professionals looking to refresh their understanding. Questions covering interrupt vectors and addressing modes.Insights into DSP architecture and instruction sets.Special features relevant to DSPs in assemblers.","img":"https:/images/course1.png"}

More Quizzes

PS - 1

1261361

PS - 2

1051011

Top Design Trends 2023 - Radiant Gradients

6343

Ang

17822

Free AP Psych Review Games: Practice

201025777

Law and Public Policy

15822242

Discover Your Perfect Dragon Match: What Dragon Are You?

201025314

Can You Ace the NCLEX Respiratory? Pneumonia & TB

201028150

Can You Ace the Total Drama Island: The Big Sleep?

201058984

Quiz Plural Mastery: Ace the Plural Nouns Test

201050843

Free Wine & Spirits Knowledge Assessment

201022242

Crunchy vs Silky Mom: Discover Your Mom's Style

201027301