Electronics Knowledge Quiz

Electronics Knowledge Quiz

Test your knowledge of electronics with our comprehensive quiz! With 62 challenging questions, this quiz covers a wide range of topics from circuit design to digital logic.

Challenge yourself and see how well you understand:

- Printed Circuit Boards (PCBs)

- Logic Gates and Fun

ctions - Capacitance and Resistors

- Digital Integrated Circuits (ICs)

SMD (Surface Mount Device) u odnosu TH (Through Hole) komponente, omogucavaju gustinu pakovanja na dvoslojne PCB (Printed Circuit Board):

Manju

Istu

Vecu

2. Direktni konektori (Edge) su u odnosu na Indirektne (Pin) po pitanju pouzdanosti:

Losiji

Isti

Bolji

3. Proizvodni troskovi (material I ugradnja) su za indirektne konektore (Pin) u odnosu na direktne konektore(Edge)

Manji

Isti

Veci

4. Za busenje rupa na dvoslojnim stampanim plocama sa metalizovanim rupama se koriste stabilne busilice sa brojem obrtaja:

200-300 rpm

2,000-3,000 rpm

20,000-30,000 rpm

5. Za busenje rupa na cetvoroslojnim stampanim plocama sa metalizovanim rupama se koriste stabilne busilice sa brojem obrtaja:

500-600 rpm

5,000-6,000 rpm

50,000-60,000 rpm

6. Keramicki kondenzatori se koriste za filtriranje napajanja digitalnih integrisanih kola zbog toga sto imaju:

Malu sopstvenu induktivnost

Veliku kapacitivnost

Veliki radni napon

7. Bipolarni NPN transistor se koristi u spoju sa zajednickim emiterom u prekidackom rezimu rada. Sa smanjenjem vrednosti kolektorskog otpornika Rc vreme zakocenja (izlaska iz zasicenja) se:

Smanjuje

Ne menja

Povecava

8. Da bi se realizovala bilo koja logicka funkcija, dovoljno je da raspolazemo sa kolima tipa:

Dvoulazno NAND

Dvoulazno AND

Dvoulazno OR

9. Logicka kola sa tri stanja na svojim izlazima, u zavisnosti od stanja ulaza I kontrolnih signala, daju:

-1, 0, 1

0, 1, 2

0, 1, HZ

10. EXOR logicka kola, u poredjenju sa OR I AND logickim kolima imaju kasnjenje:

Manje

Isto

Vece

11. EXNOR logicka kola, u poredjenju sa NOR I NAND logickim kolima imaju kasnjenje:

Vece

Isto

Manje

12. Logicki izlaz Smit triger bafera je Vout=1 za Vin>V2, a Vout=0 za Vin<V1. Kakav je odnos V1 I V2?

V1<V2

V1=V2

V1>V2

13. Vremenska konstanta za RC kolo je definisana kao:

Tau=R/C

Tau=R*C

Tau=C/R

14. Jednacina za punjenje kondenzatora preko otpornika R glasi:

U(t)=U(1-e^1/t)

U(t)=U(1+e^1/t)

U(t)=Ue^1/t

15.Jednacina za praznjenje kondenzatora preko otpornika R glasi:

U(t)=U(1-e^1/t)

U(t)=U(1+e^1/t)

U(t)=Ue^1/t

16.Kondenzator koji se puni preko otpornika sa vremenskom konstantom tau, se napuni na preko 99% vrednosti napona nakon vremena:

T=0.5tau

T=5tau

T=50tau

17.Kondenzator koji se puni preko otpornika sa vremenskom konstantom tau, se napuni na preko 99,99% vrednosti napona nakon vremena:

T=1tau

T=10tau

T=100tau

18.Kondenzator koji se puni preko otpornika sa vremenskom konstantom tau, se napuni na preko 50% vrednosti napona nakon vremena:

T=0.7tau

T=1.4tau

T=2.8tau

19.Kondenzatorske pumpe se koriste:

Iskljucivo za povecanje napona

Za povecanje napona ili za promenu polariteta napona

Iskljucivo za promenu polariteta napona

20.Preporuceni radni napon za digitalna integrisana kola u HC tehnologiji je

2V-6V

3V-18V

4.5V-5.5V

21.Radni temperaturni opseg za standardna, komercijalna, digitalna integrisana kola u HC tehnologiji je:

-40`C do +85`C

0`C -> 75`C

-55`C do +125`C

22.Maksimalni, garantovani, napon logicke nule za standardna digitalna integrisana kola u HC tehnologiji je:

0.8V

30% Vdd

50% Vdd

23.Minimalni, garantovani, napon logicke jedinice za standardna digitalna integrisana kola u HC tehnologiji je:

2V

50% Vdd

70% Vdd

24.Ulazna kapacitivnost za standardna digitalna integrisana kola u HC tehnologiji je reda:

0.5pF

5pF

50pF

25.Ulazna kapacitivnost za standardna digitalna integrisana kola u HC tehnologiji je reda:

Manja od 10k

Oko 100k

Veca od 1M

26.Vreme kasnjenja signala kroz standardna digitalna integrisana kola, tipa dvoulazno NI kolo, invertor, dvilazno NILI kolo, u HC tehnologiji je reda:

0.1ns

10ns

100ns

27.Neiskorisceni ulazi digitalnih integrisanih logickih kola, u HC tehnologiji, se vezuju na:

Vss

Vss ili Vdd, u zavisnosti od f-je

Vdd

28.Potrosnja, discipacija, digitalnih integrisanih logickih kola, u HC tehnologiji, se sa povecanjem radne ucestanosti:

Smanjuje

Ne menja

Povecava

29.Potrosnja, discipacija, digitalnih integrisanih logickih kola, u HC tehnologiji, se sa smanjenjem radnog napona:

Smanjuje

Ne menja

Povecava

30.Logicka kola sa open drain izlazom, u zavisnosti od stanja ulaza, daju:

0, HZ

1, HZ

0, 1

31.Kod wired or logike realizovane sa open drain logickim kolima na izlas se:

Vezuje pull up otpornik

Vezuje pull down otpronik

Ne vezuje otpornik

32.Oscilator sa kristalom kvarca koji osciluje na paralelnoj rezonantnoj ucestanosti ima tacnost:

1-2 ppm

10-20 ppm

100-200 ppm

33.Sat realnog vremena je realizovan sa kvarcnim oscilatorom. Tacnost ucestanosti je 100 ppm. Ovako realizovan sat gresi mesecno:

20-30 s

200-300 s

2,000-3,000 s

34.SR flip-flop je realizovan sa dva dvoulazna NI kola u HC tehnologiji. Da bi flip-flop promenio stanje potrebno je na odgovarajuci ulaz dovesti impuls minimalnog trajanja oko:

0.2 ns

2 ns

20 ns

35.SR flip-flop je realizovan sa dva dvoulazna NOR kola u HC tehnologiji. Da bi flip-flop promenio stanje potrebno je na odgovarajuci ulaz dovesti impuls minimalnog trajanja oko:

2 ns

20 ns

200 ns

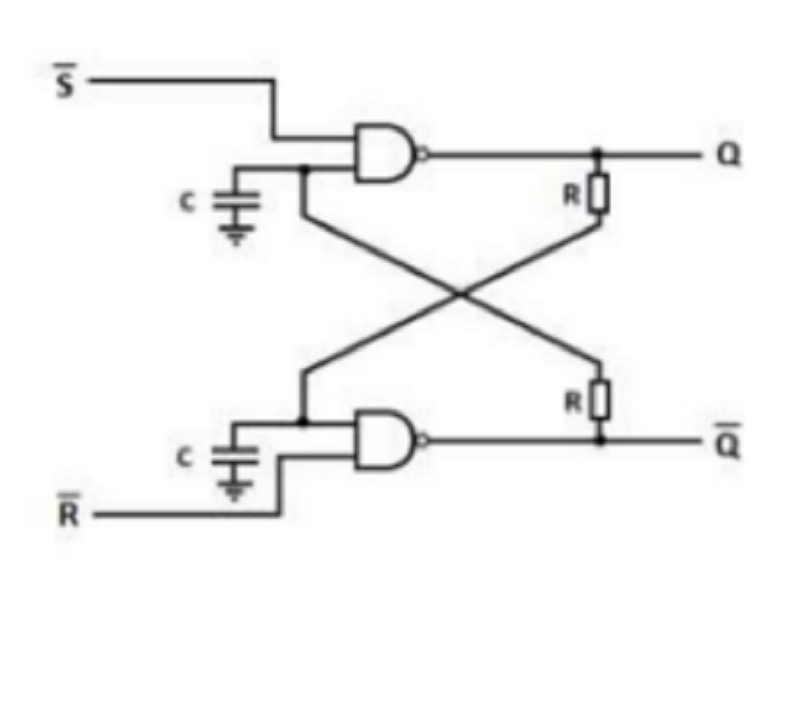

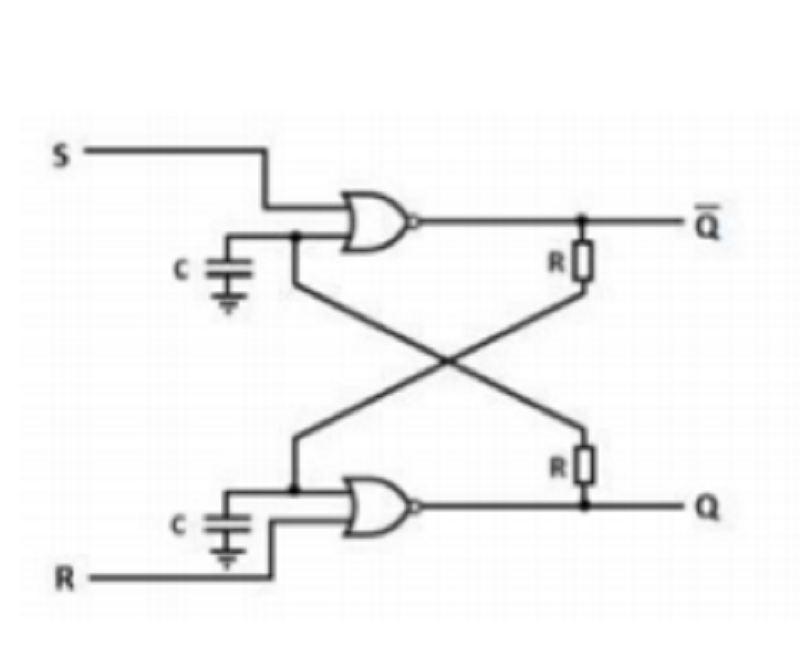

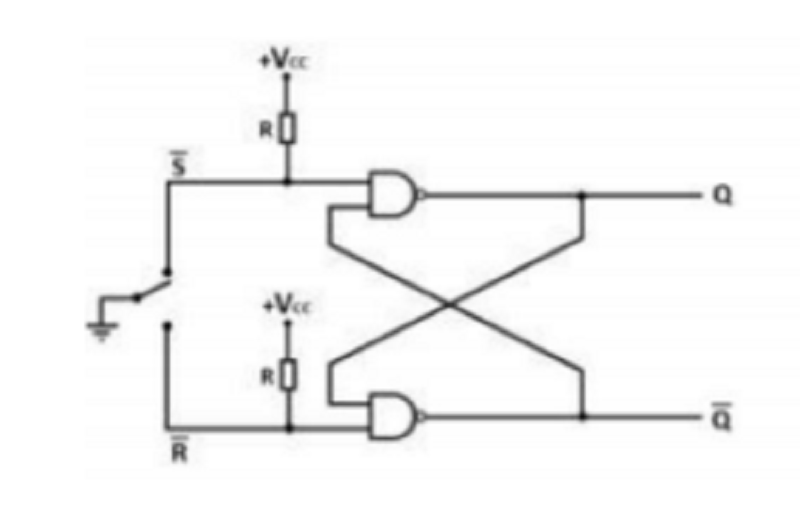

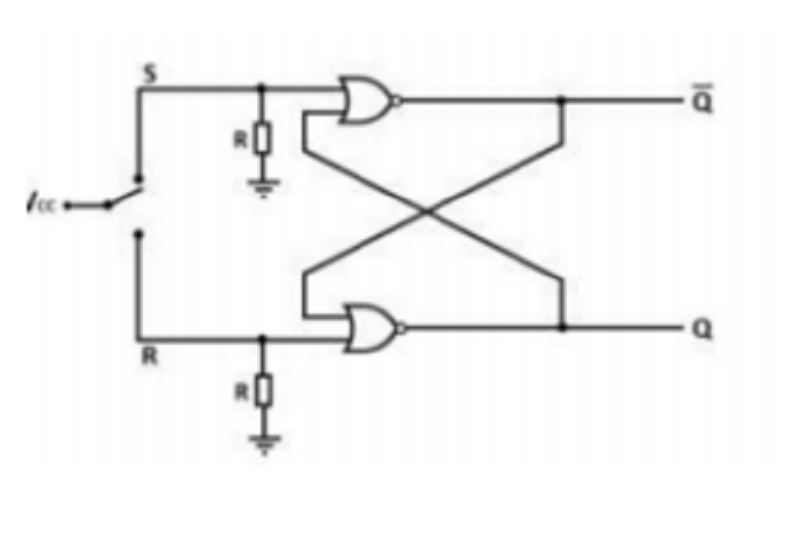

Zaštita RS flip flpa sa NI kolima od delovanja kratkotrajnih smetnji na ulazima sa povratnom spregom

Zaštita RS flip flpa sa NILI kolima od delovanja kratkotrajnih smetnji na ulazima sa povratnom spregom

Zaštita RS flip flpa sa NI kolima od delovanja kratkotrajnih smetnji na ulazima

Zaštita RS flip flpa sa NILI kolima od delovanja kratkotrajnih smetnji na ulazima

Zaštita RS flip flpa sa NI kolima od delovanja kratkotrajnih smetnji na ulazima sa povratnom spregom

Zaštita RS flip flpa sa NILI kolima od delovanja kratkotrajnih smetnji na ulazima sa povratnom spregom

Zaštita RS flip flpa sa NI kolima od delovanja kratkotrajnih smetnji na ulazima

Zaštita RS flip flpa sa NILI kolima od delovanja kratkotrajnih smetnji na ulazima

Zaštita RS flip flpa sa NI kolima od delovanja kratkotrajnih smetnji na ulazima sa povratnom spregom

Zaštita RS flip flpa sa NILI kolima od delovanja kratkotrajnih smetnji na ulazima sa povratnom spregom

Zaštita RS flip flpa sa NI kolima od delovanja kratkotrajnih smetnji na ulazima

Zaštita RS flip flpa sa NILI kolima od delovanja kratkotrajnih smetnji na ulazima

Zaštita RS flip flpa sa NI kolima od delovanja kratkotrajnih smetnji na ulazima sa povratnom spregom

Zaštita RS flip flpa sa NILI kolima od delovanja kratkotrajnih smetnji na ulazima sa povratnom spregom

Zaštita RS flip flpa sa NI kolima od delovanja kratkotrajnih smetnji na ulazima

Zaštita RS flip flpa sa NILI kolima od delovanja kratkotrajnih smetnji na ulazima

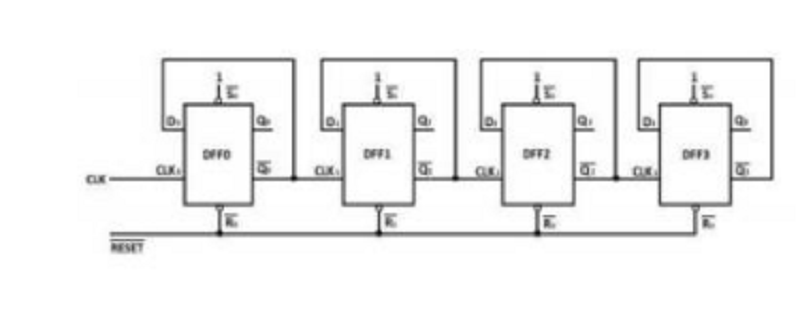

Četvorobitni asinhroni brojaĝ u napred sa okidanjem na uzlaznoj icvici Clock impulsa

Četvorobitni asinhroni brojaĝ u napred sa okidanjem na silaznoj ivici Clock impulsa

Četvorobitni asinhroni brojaĝ u nazad sa okidanjem na uzlaznoj ivici Clock impulsa

Četvorobitni asinhroni brojaĝ u nazad sa okidanjem na silaznoj ivici Clock impulsa

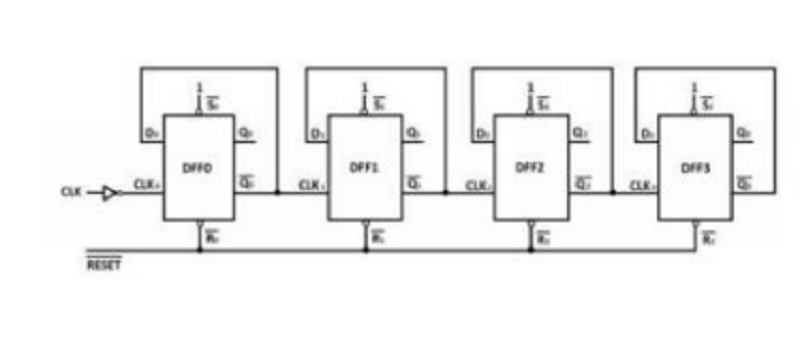

Četvorobitni asinhroni brojaĝ u napred sa okidanjem na uzlaznoj icvici Clock impulsa

Četvorobitni asinhroni brojaĝ u napred sa okidanjem na silaznoj ivici Clock impulsa

Četvorobitni asinhroni brojaĝ u nazad sa okidanjem na uzlaznoj ivici Clock impulsa

Četvorobitni asinhroni brojaĝ u nazad sa okidanjem na silaznoj ivici Clock impulsa

Četvorobitni asinhroni brojaĝ u napred sa okidanjem na uzlaznoj icvici Clock impulsa

Četvorobitni asinhroni brojaĝ u napred sa okidanjem na silaznoj ivici Clock impulsa

Četvorobitni asinhroni brojaĝ u nazad sa okidanjem na uzlaznoj ivici Clock impulsa

Četvorobitni asinhroni brojaĝ u nazad sa okidanjem na silaznoj ivici Clock impulsa

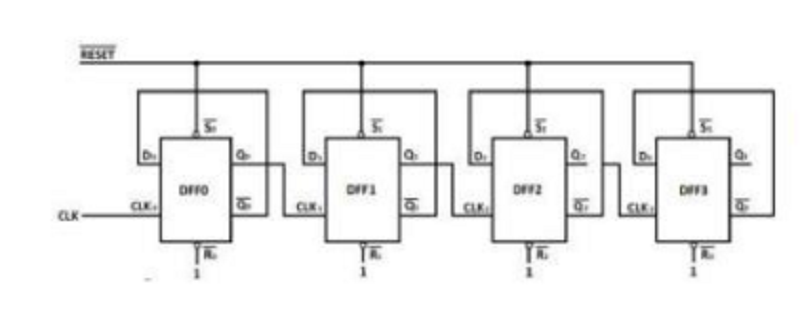

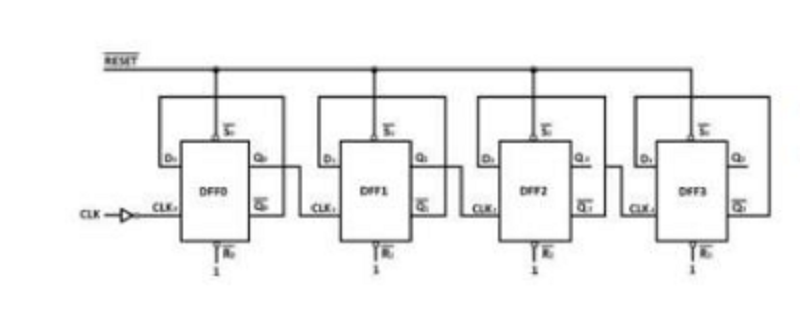

Četvorobitni asinhroni brojaĝ u napred sa okidanjem na uzlaznoj icvici Clock impulsa

Četvorobitni asinhroni brojaĝ u napred sa okidanjem na silaznoj ivici Clock impulsa

Četvorobitni asinhroni brojaĝ u nazad sa okidanjem na uzlaznoj ivici Clock impulsa

Četvorobitni asinhroni brojaĝ u nazad sa okidanjem na silaznoj ivici Clock impulsa

Detekcija zadanog stanja (5) pomodu ĝetvorobitnog asinhronog brojaĝa u napred; okidanje uzlaznom ivicom.

Detekcija zadanog stanja (6) pomodu ĝetvorobitnog asinhronog brojaĝa u napred; okidanje silaznom ivicom.

Detekcija zadanog stanja (10) pomodu ĝetvorobitnog asinhronog brojaĝa u napred; okidanje uzlaznom ivicom.

Detekcija zadanog stanja (12) pomodu ĝetvorobitnog asinhronog brojaĝa u napred; okidanje silaznom ivicom.

Detekcija zadanog stanja (5) pomodu ĝetvorobitnog asinhronog brojaĝa u napred; okidanje uzlaznom ivicom.

Detekcija zadanog stanja (6) pomodu ĝetvorobitnog asinhronog brojaĝa u napred; okidanje silaznom ivicom.

Detekcija zadanog stanja (10) pomodu ĝetvorobitnog asinhronog brojaĝa u napred; okidanje uzlaznom ivicom.

Detekcija zadanog stanja (12) pomodu ĝetvorobitnog asinhronog brojaĝa u napred; okidanje silaznom ivicom.

Detekcija zadanog stanja (5) pomodu ĝetvorobitnog asinhronog brojaĝa u napred; okidanje uzlaznom ivicom.

Detekcija zadanog stanja (6) pomodu ĝetvorobitnog asinhronog brojaĝa u napred; okidanje silaznom ivicom.

Detekcija zadanog stanja (10) pomodu ĝetvorobitnog asinhronog brojaĝa u napred; okidanje uzlaznom ivicom.

Detekcija zadanog stanja (12) pomodu ĝetvorobitnog asinhronog brojaĝa u napred; okidanje silaznom ivicom.

Detekcija zadanog stanja (5) pomodu ĝetvorobitnog asinhronog brojaĝa u napred; okidanje uzlaznom ivicom.

Detekcija zadanog stanja (6) pomodu ĝetvorobitnog asinhronog brojaĝa u napred; okidanje silaznom ivicom.

Detekcija zadanog stanja (10) pomodu ĝetvorobitnog asinhronog brojaĝa u napred; okidanje uzlaznom ivicom.

Detekcija zadanog stanja (12) pomodu ĝetvorobitnog asinhronog brojaĝa u napred; okidanje silaznom ivicom.

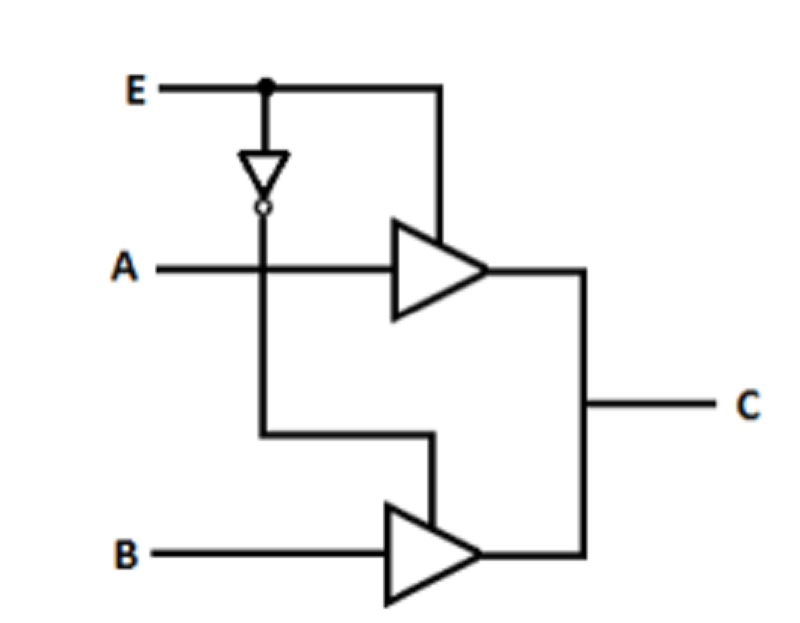

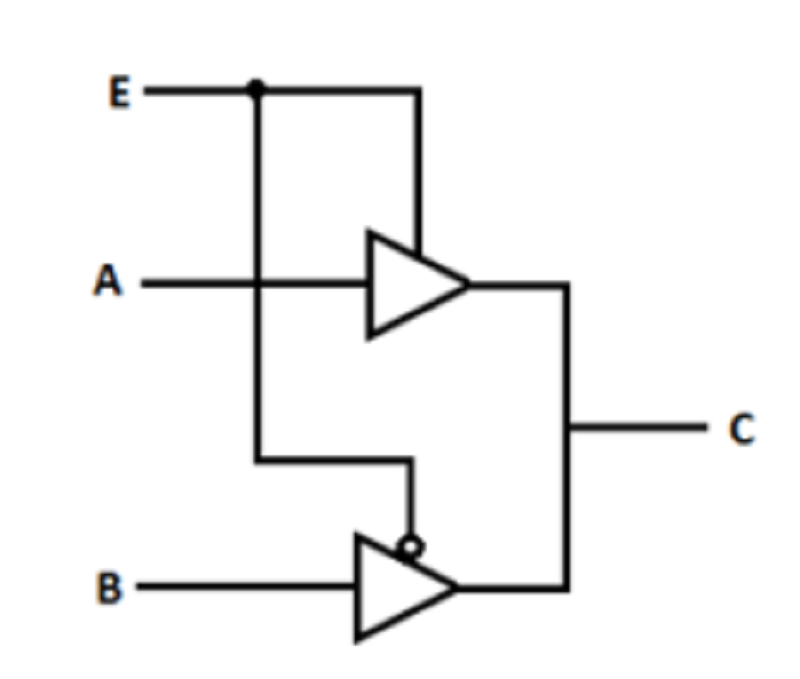

Realizacija funkcije C=A kada je E=1, a C=B kada je E=0 primenom invertora I nenvertujućih tri stejt bafera koji su aktivni kada je EN=”1”.

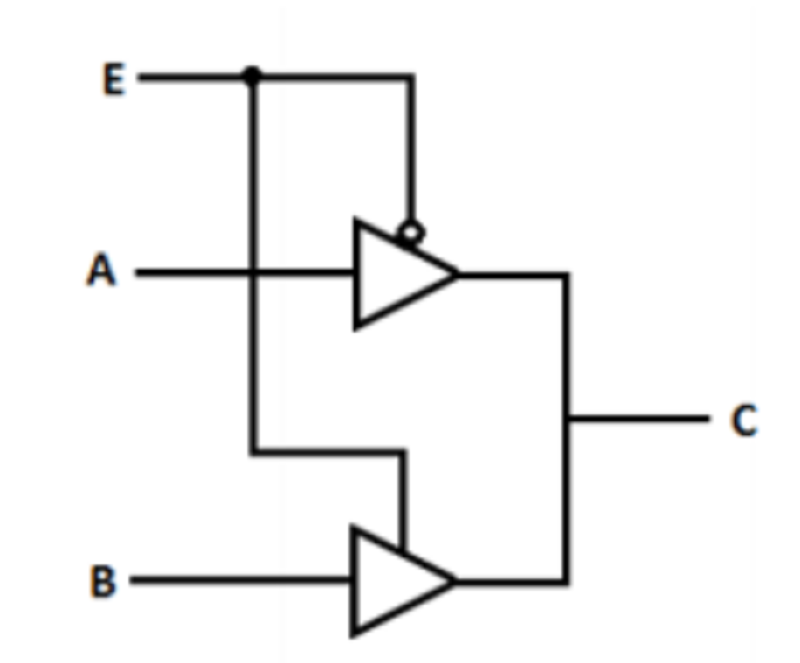

Realizacija funkcije C=A kada je E=1, a C=B kada je E=0 primenom oba tipa neinvertujućih stejt bafera.

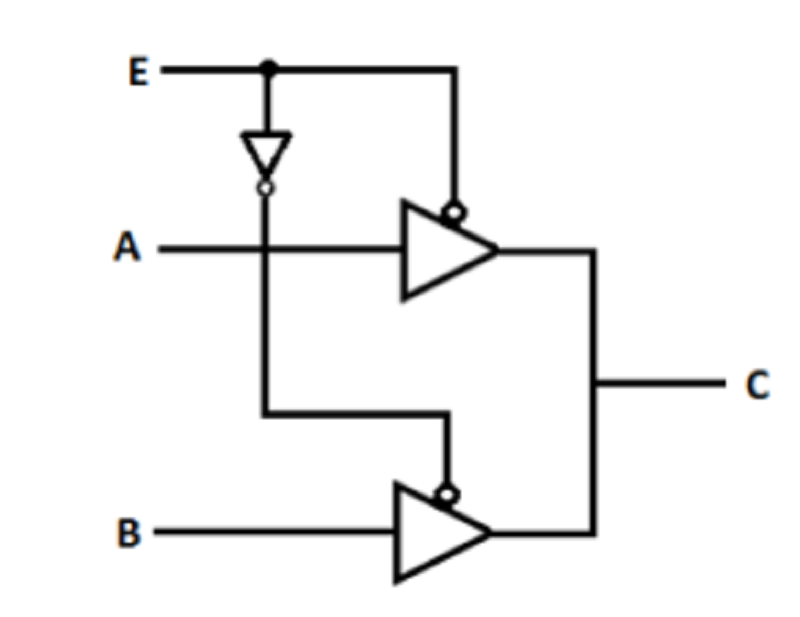

Realizacija funkcije C=A kada je E=0, a C=B kada je E=1 primenom invertora I neinvertujućih tri stejt bafera koji su aktivni kada je EN=”0”.

Realizacija funkcije C=A kada je E=0, a C=B kada je E=1 primenom oba tipa neinvertujućih tri stejt bafera.

Realizacija funkcije C=A kada je E=1, a C=B kada je E=0 primenom invertora I ninvertujućih tri stejt bafera koji su aktivni kada je EN=”1”.

Realizacija funkcije C=A kada je E=1, a C=B kada je E=0 primenom oba tipa neinvertujućih stejt bafera.

Realizacija funkcije C=A kada je E=0, a C=B kada je E=1 primenom invertora I neinvertujućih tri stejt bafera koji su aktivni kada je EN=”0”.

Realizacija funkcije C=A kada je E=0, a C=B kada je E=1 primenom oba tipa neinvertujućih tri stejt bafera.

Realizacija funkcije C=A kada je E=1, a C=B kada je E=0 primenom invertora I ninvertujućih tri stejt bafera koji su aktivni kada je EN=”1”.

Realizacija funkcije C=A kada je E=1, a C=B kada je E=0 primenom oba tipa neinvertujućih stejt bafera.

Realizacija funkcije C=A kada je E=0, a C=B kada je E=1 primenom invertora I neinvertujućih tri stejt bafera koji su aktivni kada je EN=”0”.

Realizacija funkcije C=A kada je E=0, a C=B kada je E=1 primenom oba tipa neinvertujućih tri stejt bafera.

Realizacija funkcije C=A kada je E=1, a C=B kada je E=0 primenom invertora I ninvertujućih tri stejt bafera koji su aktivni kada je EN=”1”.

Realizacija funkcije C=A kada je E=1, a C=B kada je E=0 primenom oba tipa neinvertujućih stejt bafera.

Realizacija funkcije C=A kada je E=0, a C=B kada je E=1 primenom invertora I neinvertujućih tri stejt bafera koji su aktivni kada je EN=”0”.

Realizacija funkcije C=A kada je E=0, a C=B kada je E=1 primenom oba tipa neinvertujućih tri stejt bafera.

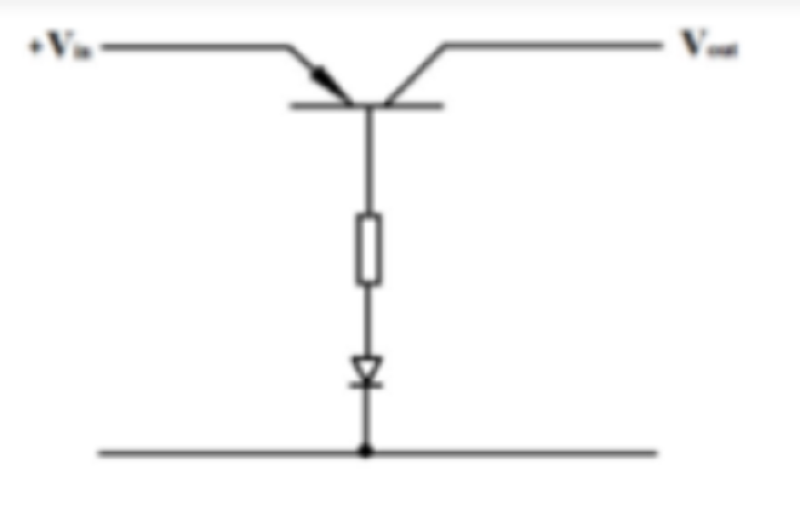

Kolo za zaštitu od pogrešnog polariteta sa bipolarnim tranzistorom.

Kolo za zaštitu od pogrešnog polariteta sa MOSFET-om.

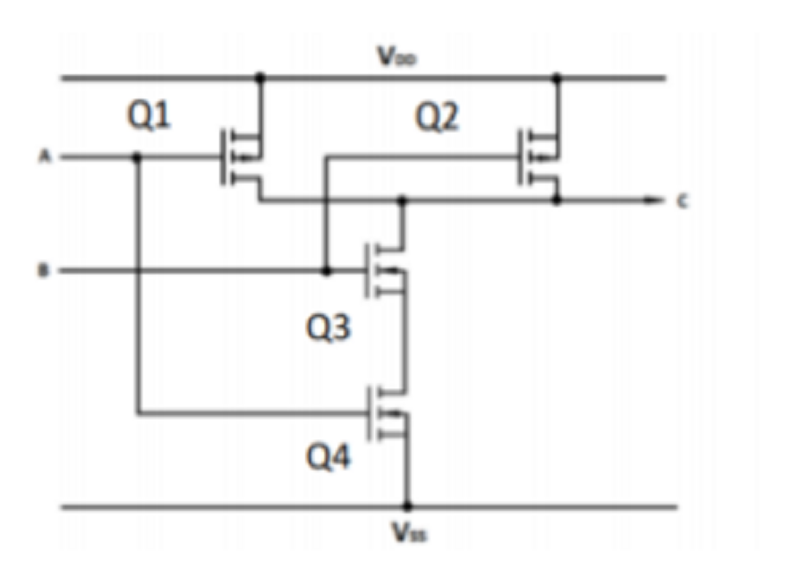

Realizacija invertora u HC (high-speed CMOS) tehnologiji

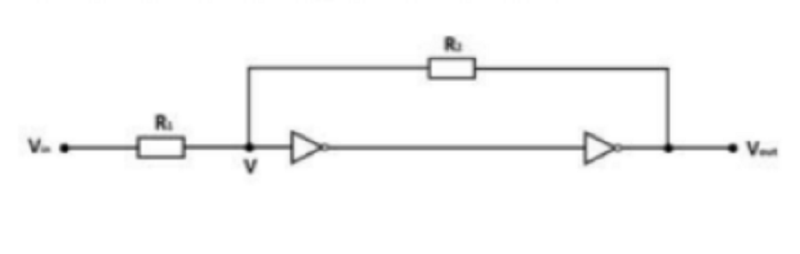

Šmit triger sa invertorima

Šmit triger sa invertorima

Realizacija invertora u HC (high-speed CMOS) tehnologiji

Kolo za zaštitu od pogrešnog polariteta sa MOSFET-om.

Kolo za zaštitu od pogrešnog polariteta sa bipolarnim tranzistorom.

Šmit triger sa invertorima

Realizacija invertora u HC (high-speed CMOS) tehnologiji

Kolo za zaštitu od pogrešnog polariteta sa MOSFET-om.

Kolo za zaštitu od pogrešnog polariteta sa bipolarnim tranzistorom.

Realizacija invertora u HC (high-speed CMOS) tehnologiji

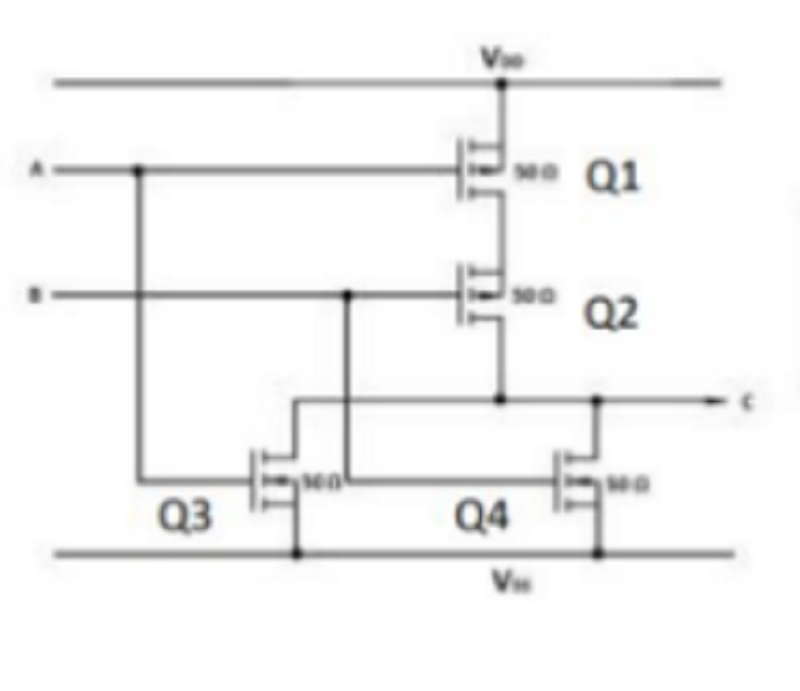

Realizacija dvoulaznog NOR kola u HC tehnologiji

Realizacija dvoulaznog NAND kola u HC tehnologiji

Šmit triger sa invertorima

Realizacija invertora u HC (high-speed CMOS) tehnologiji

Realizacija dvoulaznog NOR kola u HC tehnologiji

Realizacija dvoulaznog NAND kola u HC tehnologiji

Šmit triger sa invertorima

Realizacija invertora u HC (high-speed CMOS) tehnologiji

Realizacija dvoulaznog NOR kola u HC tehnologiji

Realizacija dvoulaznog NAND kola u HC tehnologiji

Šmit triger sa invertorima

Realizacija invertora u HC (high-speed CMOS) tehnologiji

Šmit triger sa invertorima

Kolo za zaštitu od pogrešnog polariteta sa MOSFET-om.

Realizacija dvoulaznog NOR kola u HC tehnologiji

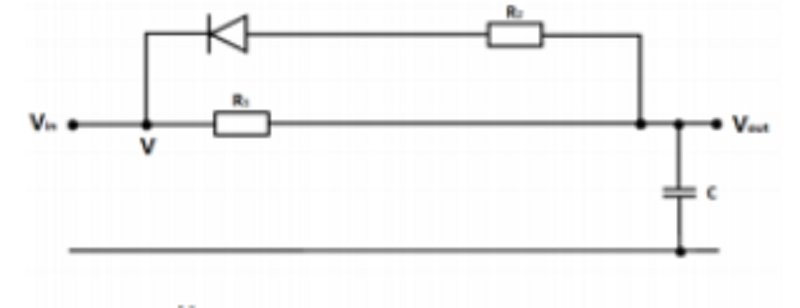

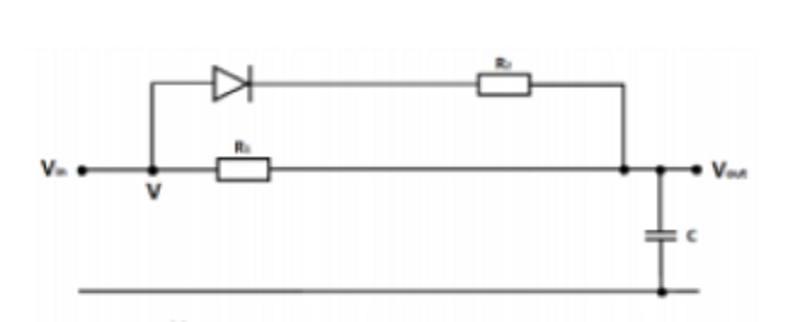

Nesimetriĝno kolo za kasnjenje/integraciju kod koga je vreme punjenja kondezatora duže od vremena pražnjenja

Nesimetriĝno kolo za kasnjenje/integraciju kod koga je vreme punjenja kondezatora kraće od vremena pražnjenja

Šmit triger sa invertorima

Realizacija dvoulaznog NOR kola u HC tehnologiji

Nesimetriĝno kolo za kasnjenje/integraciju kod koga je vreme punjenja kondezatora duže od vremena pražnjenja

Nesimetriĝno kolo za kasnjenje/integraciju kod koga je vreme punjenja kondezatora kraće od vremena pražnjenja

Šmit triger sa invertorima

Realizacija dvoulaznog NOR kola u HC tehnologiji

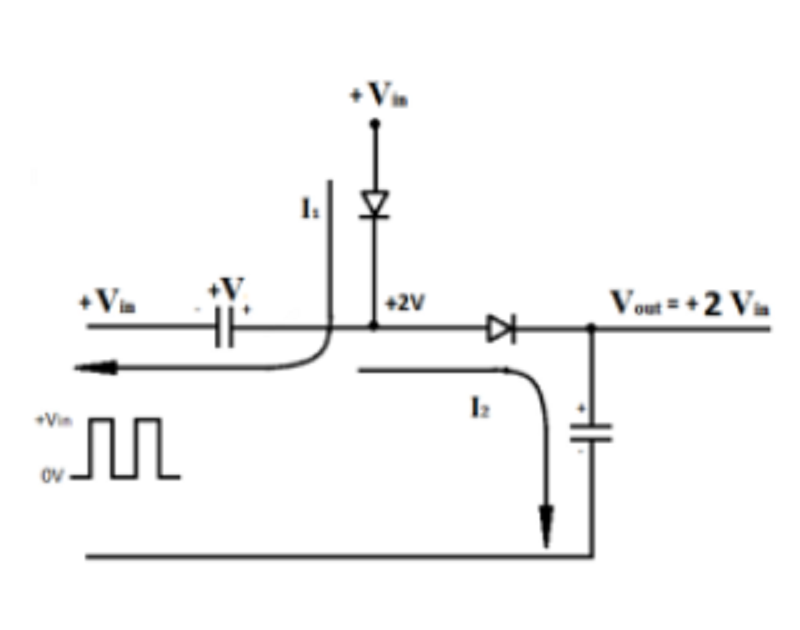

Kondezatorska pumpa za udvajanje napona

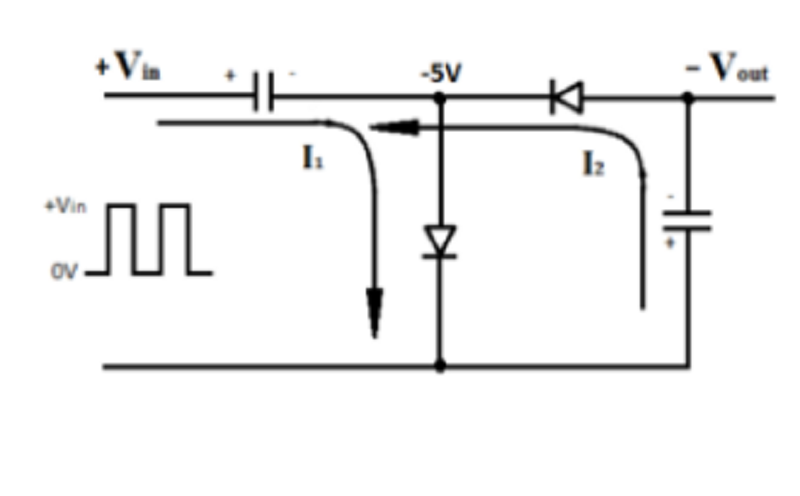

Kondezatorska pumpa za promenu polariteta napona

Nesimetriĝno kolo za kasnjenje/integraciju kod koga je vreme punjenja kondezatora kraće od vremena pražnjenja

Nesimetriĝno kolo za kasnjenje/integraciju kod koga je vreme punjenja kondezatora duže od vremena pražnjenja

Kondezatorska pumpa za udvajanje napona

Kondezatorska pumpa za promenu polariteta napona

Nesimetriĝno kolo za kasnjenje/integraciju kod koga je vreme punjenja kondezatora kraće od vremena pražnjenja

Nesimetriĝno kolo za kasnjenje/integraciju kod koga je vreme punjenja kondezatora duže od vremena pražnjenja

{"name":"Electronics Knowledge Quiz", "url":"https://www.quiz-maker.com/QPREVIEW","txt":"Test your knowledge of electronics with our comprehensive quiz! With 62 challenging questions, this quiz covers a wide range of topics from circuit design to digital logic. Challenge yourself and see how well you understand: Printed Circuit Boards (PCBs)Logic Gates and FunctionsCapacitance and ResistorsDigital Integrated Circuits (ICs)","img":"https:/images/course3.png"}

More Quizzes

MKR

582976

Revit MEP - Masinstvo

10511

Metodologia de Pesquisa - Aula 04

9430

Bio Unit/2

840

Earth Day True or False: Test Your Eco IQ Now!

201052784

Can You Conquer These National Geography Bee Questions?

201031115

Which Earth's Layer Is the Most Dense? Free

201040737

Free AP Gopo Unit 1 Test

201022457

Ultimate Gordon Ramsay: Test Your Chef Mastery

201058314

HiSET Social Studies Practice Test: Ace Your Knowledge Now

201059902

What Should I Do? Discover Your Perfect Activity Now

201023325

Free Ultimate Television Show Trivia

201021227