Dragan regele fitelor

Dragan Regele Fitelor Quiz

Testați-vă cunoștințele despre proiectarea circuitelor și tehnologiile VLSI cu acest quiz menit să evalueze înțelegerea lor. Acesta abordează subiecte precum simularea, proiectarea cipurilor și metode de verificare.

Întrebările sunt variate și se bazează pe informații teoretice și practice. Verificați-vă nivelul de expertiză și învățați lucruri noi!

Cum se definesc celulele parametrizate: (pag 66)

A.Celule care se pot adapta automat cerintelor

B.Celule digitale

C.Celule analogice

D.Celule nemodificabile

E.Fara raspuns

Compararea nelist-urilor se poate baza pe: (pag 272)

A.Izomorfismul grafurilor

B.Euristici

C.Algoritmi genetici

D.Cautarea binara

E.Fara raspuns

Simularea analogica se poate folosi pentru: (pag 169)

A.Pentru circuitele cu semnale mixte

B.Doar pentru circuitele analogice propriu-zise

C.Pentru circuitele digitale

D.Pentru simulare comportamentala

E.Fara raspuns

Care sunt problemele cu care se confrunta proiectarea VLSI: (pag 6)

A.Cerinte contradictorii(viteza, putere, arie)

B.Specificatii care se schimba si/sau evolueaza

C.Ciclu lung de proiectare

D.Necesitatea reusitei de la prima incercare

E.Fara raspuns

Pentru circuitul din figura, coada cu evenimente ca cuprinde pe rand: (pag 242)

A. La 0 (A 1 t)(D 0 t) La t+ (E 0 t+1)(C 0 t+1)(F X t+1)(B X t+1) La (t+1)+ (F 1 t+2)(B 1 t+2) La (t+2)+ (E 0 t+3)(C 0 t+3) La (t+3) gol

B. La 0 (A 1 t)(C 0 t) La t+ (E 0 t+1)(C 0 t+1)(F X t+1)(B X t+1) La (t+1)+ (E 1 t+2)(B 1 t+2) La (t+2)+ (E 0 t+3)(A 0 t+3) La (t+3) gol

C. La 0 (A 1 t)(D 0 t) La t+ (E 0 t+1)(C 0 t+1)(F X t+1)(B X t+1) La (t+1)+ (F 1 t+2)(B 1 t+2) La (t+2)+ (F 0 t+3)(B 0 t+3) La (t+3) gol

D. La 0 (A 1 t)(C 0 t) La t+ (E 0 t+1)(B 0 t+1)(F X t+1)(C X t+1) La (t+1)+ (E 1 t+2)(B 1 t+2) La (t+2)+ (E 0 t+3)(A 0 t+3) La (t+3) gol

E.Fara raspuns

Fiecare: (pag 121)

A.Nod poate avea oricate conexiuni

B.Arc conecteaza intre ele oricate noduri

C.Nod poate avea exact 2 conexiuni

D.Arc conecteaza intre ele exact 2 noduri

E.Fara raspuns

In metoda “Waveform Relaxation”: (pag 171-173)

A.Se ignora temporar cuplajul dintre noduri

B.Este eficienta in special pentru circuitele digitale

C.Se liniarizeaza circuitul

D.Se rezolva ecuatiile pornind de la sursele de semnal si urmarind directia de propagare a semnalelor prin circuit

E.Fara raspuns

Care sunt caracteristici ale proiectarii cipurilor: (pag 55)

A.Utilizarea de circuite standard

B.Utilizarea ierarhiei pentru a controla complexitatea

C.Utilizarea conectivitatii(folosim circuite electronice)

D.Geometria finita(pe cip) este lipsita de ierarhie

E.Fara raspuns

Care sunt modurile de implementare a interconexiunilor: (pag 77)

A.Termic

B.Electric

C.Explicit, prin terminale

D.Implicit, prin alaturare-suprapunere

E.Fara raspuns

Inainte de extragerea schemei din layout este indicat sa se faca: (pag 266)

A.ERC

B.Simulare

C.DRC

D.Generarea vectorilor de test

E.Fara raspuns

Care sunt primitivele pentru layout: (pag 82)

A.Dreptunghiuri

B.Texte

C.Simboluri

D.Poligoane

E.Fara raspuns

Cautarea poate fii accelerata prin alegerea unui punct de start convenabil astfel: (pag 134)

A.Se cauta de la sfarsitul listei

B.Ultimul obiect selectat daca se cauta obiectele pornind de la un set de coordonate

C.Se cauta de la inceputul listei

D.Se porneste de la obiectul curent daca se cauta vecinii sai

E.Fara raspuns

La implementarea functiei de anulare a modificarilor “undo” trebuie sa: (pag 115)

A.Memoram modificarile in ordinea in care s-au produs

B.Economisim resurse in detrimentul functionalitatii

C.Operatiunile de stergere trebuie sa memoreze tot continutul obiectului sters

D.Permite anularea unei singure modificari

E.Fara raspuns

Care este reprezentarea preferata a geometriilor: (pag 132)

A.Arbori de tip R (“R-trees”)

B.Liste dublu inlantuite

C.Arbori binari

D.”corner stitching”

E.Fara raspuns

Prototipurile celulelor se preiau din: (pag 117)

A.Mediul de proiectare

B.Regulile de proiectare electrica

C.Biblioteci de celule

D.Regulile de proiectare fizica

E.Fara raspuns

Care sunt domenii de reprezentare din diagrama Gajsi: (pag 11)

A.Analogic

B.Digital

C.Structural

D.Comportamental

E.Fara raspuns

Care dintre instrumentele de mai jos se folosesc in sinteza: (pag 46-49)

A.De simulare comportamentala

B.De verificare a regulilor de proiectare fizica

C.Desimulare mixta

D.De introducere a schemei electrice

E.Fara raspuns

Modificare bazei de date a proiectului implica: (pag 113)

A.Ajustarea parametrilor de model

B.Modificarea ierarhiei

C.Modificarea reprezentarii in memorie

D.Interfata speciala pentru realizarea schimbarilor

E.Fara raspuns

Care sunt etape din abordarea “Top-Down” (pag 14)

A.Definirea modulelor functionale

B.Alegerea modulelor impreuna

C.Se construiesc portile logice

D.Definirea ierarhiei proiectului

E.Fara raspuns

Care dintre urmatoarele operatii se pot folosii la verificarea bazata pe poligoane: (pag 261)

A.Si (“AND”), sau(“OR”), sau-exclusiv(“XOR”)

B.Combinare(“merge”)

C.Atinge(“touch”)

D.Expandare(“bloat”)

E.Fara raspuns

Care dintre urmatoarele sunt stiluri de proiectare 1: (pag 21)

A.La comanda(Full Custom)

B.Proiectare digitala

C.Arii de porti(Gate-Array)

D.Folosirea de semnale mixte

E.Fara raspuns

Geometriile de tip Boston permit desenare la: (pag 128)

A.Doar 45 din 45

B.Orice unghi

C.Doar structuri ortogonale

D.Doar cercuri

E.Fara raspuns

In Spice, de ce sunt necesare metode de limitare a tensiunilor si curentilor: (pag 155)

A.Pentru a evita rezultatele aberante care apar in iteratii

B.Pentru a imbunatatii rezultatele

C.Pentru a accelera convergenta

D.Pentru a simula dispozitivele speciale

E.Fara raspuns

Sortarea laturilor dupa una dintre axe se foloseste in algebra poligoanelor pentru:

A.Identificarea poligoanelor cu auto-intersectii

B.Reducerea spatiului de memorie consumat

C.Accel determinarea intersectiilor dintre poligoane

D.Stabilirea apartenentei fiecarui poligon la un layer

E.Fara raspuns

Prototipurile:

A.Descriu caracteristicile particulare ale fiecarui obiect

B.Descriu o clasa de obiecte

C.Grupeaza proprietatile comune

D.Pot fi particularizate la instantiere

E.Fara raspuns

Care este factorul de ramificatie optim din punctul de vedre al proiectantului: (pag 62)

A.5-9

B.50-100

C.10-15

D.2-3

E.Fara raspuns

Care dintre urmatoarele sunt etape din abordarea “Bottom-up” (pag 15)

A.Agregarea modulelor impreuna

B.Se construiesc cu porti logice

C.Definirea ierarhiei proiectului

D.Definirea modulelor functionale

E.Fara raspuns

Care dintre urmatoarele sunt caracteristici ale proiectarii cipurilor 2: (pag 55)

A.Utilizarea de vederi (“views”) diferite

B.Utilizarea de circuite standard

C.Folosirea strict numai de instrumente grafice

D.Geometria finala (pe cip) este ierarhica

E.Fara raspuns

Pentru modificarea bazei de date se folosesc rutine separate pentru a schimba: (pag 113)

A.Conectivitatea (crearea si stergerea de comp si conex)

B.Ierarhia (creare si stergere def de celule si instantierile)

C.Geometria (modif instantierii unui obiect)

D.Vederile (modif/actual pointerilor din baza de date)

E.Fara raspuns

Ce inseamna “PVT” (pag 18)

A. Proces, volum, timp

B.Presiune, volum, timp

C.Parametrii, variatie, timp

D.Proces, tensiune, temperatura

E.Fara raspuns

Reprezentarea circuitelor foloseste:

A.Legaturi

B.Obiecte

C.Functii

D.Liste simplu/dublu inantuite

E.Fara raspuns

Care dintre urmatoarele sunt tehnici de reducere a puterii: (pag 20)

A.Reducerea tensiunii de alimentare

B.Folosirea redundantei

C.Cresterea temperaturii

D.Reducerea numarului de noduri care comanda

E.Fara raspuns

Verificarile uzuale ale proiectelor de circuite integrate include:

A.Verificarea regulilor de proiectare electrica

B.Verificarea corespondentei schema-layout

C.Verificarea regulilor de proiectare fizica

D.Verificarea timming-ului

E.Fara raspuns

Care dintre urmatoarele sunt caracteristici ale metodologiilor de proiectare: (pag 8)

A.Abordari de proiectare “top-down”

B.Asigurarea succesului proiectarii

C.Abordari de proiectare “bottom-down”

D.Realizarea de compromisuri tehnice

E.Fara raspuns

Metodele de tip ”Steady-State Analysis” folosesc: (pag 176-180)

A.”Envelope-Following Method”

B.Newton shooting method

C.Harmonic balance

D.Integrare gear in domeniul frecventa

E.Fara raspuns

Intr-un arbore de tip R (“R-tree”) modificarea unui obiect se face prin:

A.Folosirea stivei

B.Stergere si re-insertie

C.Descompunerea in dreptunghiuri/fragmentare

D.Modificarea pointerilor

E.Fara raspuns

Un port este: (pag 121)

A.Punctul de conectare a unui arc la un nod

B.Un dispozitiv al circuitului

C.Un obiect special

D.Structura de date

E.Fara raspuns

Simularea in spice a circuitelor sau a sistemelorindependent de strucutra lor se poate face prin:

A.Descompunerea structurii in blocuri

B.Modelarea comportamentala

C.Macro-modele

D.Ecuatii diferentiale implicite

E.Fara raspuns

Dezavantajul simularii analogice:

A.Usurinta modificarii valorilor componentelor

B.Metodele numerice pot conduce la erori si ne-convergenta

C.Posibilitatea de a masura tensiuni si curenti incacesibil in circuitul real

D.Circuitele reale sunt sisteme cu constante distribuite

E.Fara raspuns

Pentru un nod sunt posibile mai multe surse de semnal simultan: (pag 76):

A.In nodurile izolate

B.In nodurile digitale

C.In nodurile scurtcircuitate

D.In nodurile analogice

E.Fara raspuns

qqq

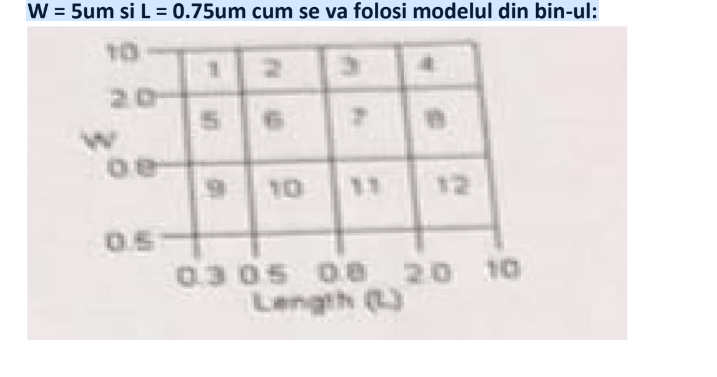

In cazul “binning” ca cel din figura de mai jos un tranzistor MOS cu W = 5um si L = 0.75um cum se va folosi modelul din bin-ul:

In cazul “binning” ca cel din figura de mai jos un tranzistor MOS cu W = 5um si L = 0.75um cum se va folosi modelul din bin-ul:A.2

B.11

C.9

D.4

E.Fara raspuns

111

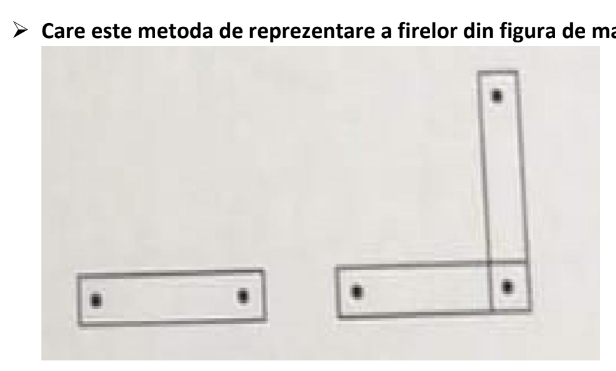

Care este metoda de reprezentare a firelor din figura de mai jos:

Care este metoda de reprezentare a firelor din figura de mai jos:A.Prin extensie cu jumatate din latime

B.Prin rotunjire

C.Prin trunchiere

D.Prin taiere la capat

E.Fara raspuns

Granularitatea mare implica:

A.Flexibilitate redusa

B.Nu influenteaza complexitatea ierarhiei

C.Complexitatea mare a ierarhiei

D.Circuite simple

E.Fara raspuns

Prototipurile:

A.Descriu o clasa de obiecte

B.Pot fi particularizate la instantiere

C.Descriu o clasa de obiecte

D.Grupeaza proprietatile comune

E.Fara raspuns

Regulile de proiectare fizica se exprima in general in:

A.Watti

B.Fara dimensiune

C.Amperi

D.Volti

E.Fara raspuns

In reprezentarea vederilor atribute de tip pointer trebuie sa contina info suplimentare privind starea sa actuala sunt:

A.Data modificarii

B.Proiectantul stie sau nu ca a aparut o modificare

C.Campuri de tip notite si comentarii

D.Pointer-ul este valid/invalid

E.Fara raspuns

Unde se consuma putere semnificativa intr-un circuit digital:

A.Traseele de alimentare

B.Incarcarea si descarcarea capacitatilor din noduri

C.Curentii de pierderi ai tranzistoarelor MOS

D.Curentii de scurtcircuit pe durata tranzitiei

E.Fara raspuns

Metoda de analiza din Spice este:

A.Metoda nodala modificata (“MNA”)

B.Metoda nodala

C.Metoda Gear

D.Metoda trapezelor

E.Fara raspuns

De ce sunt necesare tehnici “Low power”?

A.Creste frecventa de ceas -> creste puterea consumata

B.Creste numarul de porti -> creste puterea consumata

C.Scade complexitatea circuitelor

D.Raspandirea disp, portabile alim. De baterii

E.Fara raspuns

Reprezentarea circuitelor foloseste:

A.Obiecte

B.Functii

C.Liste simplu/dublu inlantuite

D.Legaturi

E.Fara raspuns

Compararea netlist-urilor se poate baza pe

A.Euristici

B.Cautari binare

C.Izomorfismul grafurilor

D.Algoritmi genetici

E.Fara raspuns

In sistemul Manhattan pentru celule sunt posibile:

A.8 orientari

B.12 orientari

C.16 orientari

D.4 orientari

E.Fara raspuns

Intr-un arbore de tip R (“R-Tree”) modificarea unui obiect se face prin:

A.Folosirea stivei

B.Descompunerea in dreptunghiuri/fragmente

C.Stergere si reinsertie

D.Modificarea pointerilor

E.Fara raspuns

In Spice analiza AC presupune:

A.Amplitudine mai mica de 25 mV

B.Semnal dreptunghiular

C.Semnal sinusoidal de o singura frecventa

D.Amplitudine suficient de mica pentru liniarizare

E.Fara raspuns

Care sunt tipurile de vederi ale circuitelor electronice:

A.De topologie

B.Electrice

C.Comportamental

D.De timp

E.Fara raspuns

Dezavantajele simularii analogice

A.Metodele numerice pot duce la erori si non-convergenta

B.Usurinta modificarii componentelor

C.Circuitele reale sunt sisteme cu constante distribuite

D.Posibilitatea de a masura tensiuni si curenti inaccesibili in circuitul real

E.Fara raspuns

Care dintre urmatoarele etape sint etape din abordarea “Bottom-Up”?

A.Definirea modulelor functionale

B.Agregarea modulelor impreuna

C.Se construiesc portile logice

D.Definirea ierarhiei proiectului

E.Fara raspuns

{"name":"Dragan regele fitelor", "url":"https://www.quiz-maker.com/QPREVIEW","txt":"Testați-vă cunoștințele despre proiectarea circuitelor și tehnologiile VLSI cu acest quiz menit să evalueze înțelegerea lor. Acesta abordează subiecte precum simularea, proiectarea cipurilor și metode de verificare.Întrebările sunt variate și se bazează pe informații teoretice și practice. Verificați-vă nivelul de expertiză și învățați lucruri noi!","img":"https:/images/course6.png"}

More Quizzes

ISM

3618131

ISM

512642

About Lenz's law!!

210

HSWG Term 2 2020

12612

Is It a Date or Hanging Out - Find Out Now

201018891

Breast Pump: Find the Right Pump for You (Free)

201019955

SAT Vocabulary Practice Test - Free College Prep

201021074

Catcher in the Rye Characters - Test Your Knowledge

201025144

Twin Facts - How Much Do You Know? Free

201028964

Which Haircut Should I Get? Free Style Match

201018373

Clip Art - Identify Icons from The Noun Project

201021570

Apple Trivia Questions - Free Apple Products

201029794

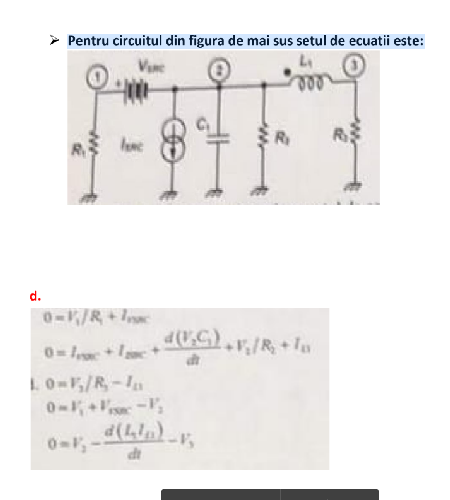

Pentru circuitul din figura, setul de ecuatii este: (pag 144)

Pentru circuitul din figura, setul de ecuatii este: (pag 144) Pentru circuitul din figura de mai sus setul de ecuatii este:

Pentru circuitul din figura de mai sus setul de ecuatii este: